enable uart2 is posiible on Omega2+??

-

Hello all,

I need to enable uart2 on Omega2+. I need 2 uarts but I wouldn't like to disable Console log on uart0.

On uart0 log, omega2-ctrl and some forums I saw there are 3 uarts (tx2/rx2 on pins 16/17), but only 2 are available.

How can I enable and use it?thanks

-

I have to say that just enabling uart2 in omega2-ctrl doesn't seem to work.

any idea? somebody did it?

-

@pablo-campos It is not possible because UART_TXD2, UART_RXD2 share GPI#O20, GPIO#21 pins respectively and those pins are not exposed on Omega2(+).

You could plug practically any cheap USB-to-Serial (3.3V or 5V TTL or even RS232 etc.) converter module in the Omega's USB Host Port instead.

-

@pablo-campos said in enable uart2 is posiible on Omega2+??:

On uart0 log, omega2-ctrl and some forums I saw there are 3 uarts (tx2/rx2 on pins 16/17), but only 2 are available.

The HLK-7866 module exposes UART2 pins, you need to compile new u-boot and modify the Kernel and then you can get UBOOT and Kernel console on UART2

-

@Gnichi-Mohamed See also Omega2S

Surface Mount Packaged version of the Omega2

-

@György-Farkas that's true

-

@pablo-campos It is possible

... so I was wrong - again

... so I was wrong - again

After this commandomega2-ctrl gpiomux set spi_s pwm01_uart2Omega2(+)'s UART2 (ttyS2) works well using GPIO16 as TX2 and GPIO17 as RX2 (8N1 default BAUD rate 9600 bps).# Omega2+ FW v0.2.2 b201 root@Omega-5BE1:~# omega2-ctrl gpiomux set spi_s pwm01_uart2 set gpiomux spi_s -> pwm01_uart2 root@Omega-5BE1:~# omega2-ctrl gpiomux get Group i2c - [i2c] gpio Group uart0 - [uart] gpio Group uart1 - [uart] gpio pwm01 Group uart2 - [uart] gpio pwm23 Group pwm0 - pwm [gpio] Group pwm1 - pwm [gpio] Group refclk - refclk [gpio] Group spi_s - spi_s gpio [pwm01_uart2] Group spi_cs1 - [spi_cs1] gpio refclk Group i2s - i2s [gpio] pcm Group ephy - [ephy] gpio Group wled - wled [gpio]I have also tried it successfully with

picocom -b 115200 /dev/ttyS2on Omega2+ and

picocom -b 115200 /dev/ttyUSB0on Ubuntu 18.4.1 LTS with an FTDI232 USB-to-3.3V Serial module.Good luck.

-

Thanks György Farkas,

Using "omega2-ctrl gpiomux set spi_s pwm01_uart2" enable the uart2 and works fine!

I was using "omega2-ctrl set uart2 uart"

and I geting:

Group i2c - [i2c] gpio

Group uart0 - [uart] gpio

Group uart1 - [uart] gpio pwm01

Group uart2 - [uart] gpio pwm23

Group pwm0 - pwm [gpio]

Group pwm1 - pwm [gpio]

Group refclk - refclk [gpio]

Group spi_s - spi_s [gpio] pwm01_uart2But didn't work. With the config that György Farkas suggested, is working!!

In fact the config of Group uart2 seems to be irrelevant.

I have:

...

Group uart2 - uart gpio [pwm23]

....

Group spi_s - spi_s gpio [pwm01_uart2]and still working...

Thanks again!

-

@pablo-campos said in enable uart2 is posiible on Omega2+??:

I was using "omega2-ctrl gpiomux set uart2 uart"

...

(omega2-ctrl gpiomux get)

Group uart2 - [uart] gpio pwm23

...

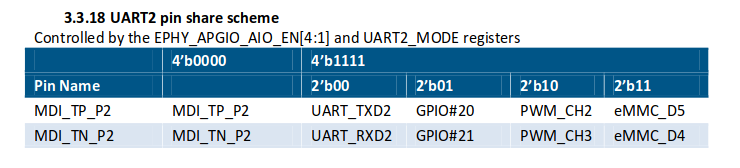

In fact the config of Group uart2 seems to be irrelevant.Here you are some details from the Mediatek MT7688 Datasheet:

3.3 Pin Sharing Schemes 3.3.1 GPIO pin share scheme --------------+-------------+----------- I/O Pad Group | Normal Mode | GPIO Mode --------------+-------------+----------- SPIS | MDI_RP_P1 | GPIO#16 | MDI_RN_P1 | GPIO#17 --------------+-------------+----------- UART2 / eMMC | MDI_TP_P2 | GPIO#20 | MDI_TN_P2 | GPIO#21``` 3.3.21 SPIS pin share scheme ----------+-----------+-----------+---------+---------------------+--------------------------- Controlled| b0000 | b1111 | EPHY_APGIO_AIO_EN bit 4:1 by +-----------+-----------+---------+---------+-----------+--------------------------- | | b00 | b01 | b10 | b11 | SPIS_MODE bit 3:2 ----------+-----------+-----------+---------+---------+-----------+--------------------------- Pin Name | ----------+-----------+-----------+---------+---------+-----------+ MDI_RP_P1 | MDI_RP_P1 | SPIS_MISO | GPIO#16 | | UART_TXD2 | MDI_RN_P1 | MDI_RN_P1 | SPIS_MOSI | GPIO#17 | | UART_RXD2 | [SPIS_MODE] PWM CH0/1 and UART2 3.3.18 UART2 pin share scheme ----------+-----------+-----------+---------+-------------------+--------------------------- Controlled| b0000 | b1111 | EPHY_APGIO_AIO_EN bit 4:1 by +-----------+-----------+---------+---------+---------+--------------------------- | | b00 | b01 | b10 | b11 | UART2_MODE bit 27:26 ----------+-----------+-----------+---------+---------+---------+--------------------------- Pin Name | ----------+-----------+-----------+---------+---------+---------+ MDI_TP_P2 | MDI_TP_P2 | UART_TXD2 | GPIO#20 | PWM_CH2 | eMMC_D5 | MDI_TN_P2 | MDI_TN_P2 | UART_RXD2 | GPIO#21 | PWM_CH3 | eMMC_D4 | [UART2_MODE] UART-Lite #2omega2-ctrl gpiomux set uart2 uartis really irrevelant on Omega2(+) but both configs should be OK on Omega2(+)S (not the same time of course).

I don't have it so I can't try the other config.

-

I am using UART1 (pins 45, 46) with python pyserial library without any utilities. All works good.