CPU_RST and VDD_FLASH

-

Re: Omega2S Reset Pin C21 shutdown instead of reset

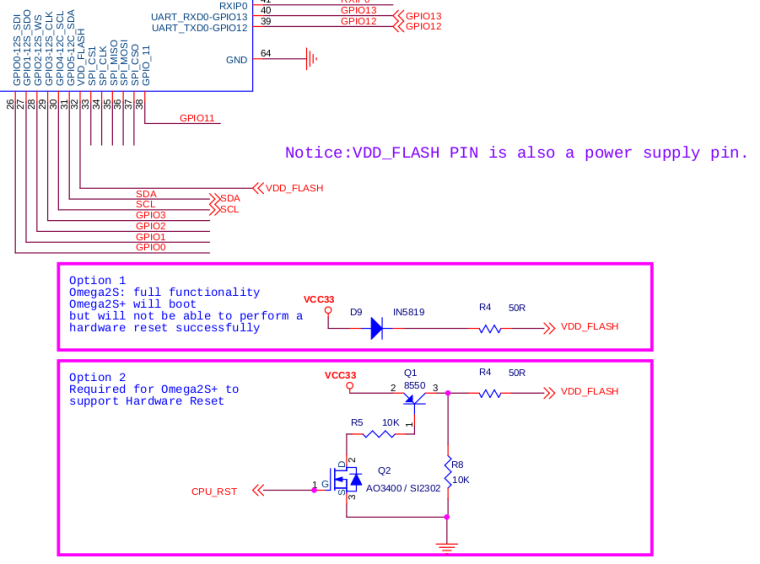

I have some issues with my Omega2S+ on a custom board. The CPU does not reboot after reset, and this HW reset circuit has been implemented.

I notice that even with Q2 (in the diagram of topic 2927) shut off (or even removed from the PCB) there is around 2V on the VDD_FLASH pin. I assume this is enough to keep the flash from resetting to 3 byte mode.

Does anyone know how to make sure the reset works?

Thanks,

Erik

-

@Erik-Hougaard said in CPU_RST and VDD_FLASH:

Re: Omega2S Reset Pin C21 shutdown instead of reset

I notice that even with Q2 (in the diagram of topic 2927) shut off (or even removed from the PCB) there is around 2V on the VDD_FLASH pin.Probanly you have applied Option 1

*and Option 2 simultaneously on your custom board.

(*or there's some similar connection between VCC33 and VDD__FLASH)

Please check your custom PCB.

Omega2S-Reference-Schematic.pdf (That Q2 is Q1 here.

-

I don't see why that would be making a lot of change, but I implemented an additional FET which shorts VDD_FLASH to ground when reset is active. Gate is connected to the drain of Q2.

It's not a solution that makes me proud, but it works.

Erik

-

It's likely you are facing one or possibly the combination of two known issues.

One is that because an incompatible 32 megabyte SPI flash was used, accessing the whole of it requires putting it in a mode incompatible with boot, so unless something resets the flash chip when the CPU does, a warm boot will fail. Most other vendors avoided this by operating their 32-megabyte flash in 4-byte address mode all the time (but that would have required different strapping for the 16 meg and 32 meg versions).

Another is that if you have anything connected, say a debug serial port, the data lines itself will keep the MT7688 alive enough that it won't do a clean power on reset . Potentially in this case you have a similar leakage path where an I/O is keeping your flash chip alive enough during the power interruption that it isn't losing the boot-incompatible 4-byte address mode state. Or you could have residual charge on a capacitor.